### (19)日本国特許庁(JP)

# (12) 特 許 公 報(B2)

(11)特許出願公告番号

特公平6-7389

(24) (44)公告日 平成6年(1994)1月26日

(51)Int.Cl.<sup>5</sup> G 0 6 F 15/70 識別記号 庁内整理番号 3 4 0 9071 - 5L

FΙ

技術表示箇所

発明の数1(全 5 頁)

(21)出願番号 特願昭59-197945

(22)出願日 昭和59年(1984)9月20日

(65)公開番号 特開昭61-75485

(43)公開日 昭和61年(1986) 4月17日 (71)出願人 999999999

オムロン株式会社

京都府京都市右京区花園土堂町10番地

(72)発明者 政木 俊道

京都府京都市右京区花園土堂町10番地 立

石電機株式会社内

(72)発明者 久野 敦司

京都府京都市右京区花園土堂町10番地 立

石電機株式会社内

(72) 発明者 坂 和彦

京都府京都市右京区花園土堂町10番地 立

石電機株式会社内

(74)代理人 弁理士 鈴木 由充

審査官 加古 進

最終頁に続く

#### (54) 【発明の名称 】 画像処理装置

## 【特許請求の範囲】

【請求項1】白黒2値化された入力パターンの輪郭線を 追跡する輪郭追跡手段を備えた画像処理装置において、 前記入力パターンを構成する2値画像データと、前記輪 郭追跡手段による輪郭追跡処理時に設定される追跡処理 データとして入力パターンの輪郭構成画素に設定される 輪郭フラグおよび次の輪郭構成画素への追跡方向に応じ て設定されるペアフラグとを、各画素毎に記憶すること が可能な画像メモリと、

セスする走査手段と、

前記走査手段によりアクセスされた各画素の 2 値画像デ ータおよび前記追跡処理データを取り込んでアクセス対 象画素が輪郭追跡処理済の入力パターンの内外いずれに 位置するかを認識する認識手段と、

前記認識手段による認識結果に基づきアクセス対象画素 を輪郭追跡処理の開始点として検出するかどうかを決定 する輪郭追跡開始点検出手段とを備えて成る画像処理装 置。

#### 【発明の詳細な説明】

<発明の技術分野>

本発明は、文字、図形等の画像入力を白黒2値化して入 カパターンを求め、この入力パターンにつき辞書等の照 合処理を実行して、未知文字等を認識する技術に関連 前記画像メモリを所定方向へ走査して各画素を順次アク 10 し、殊に本発明は、前記照合処理に先立ち、入力パター ンの輪郭線を高速度で追跡するための画像処理装置に関 する。

### <発明の背景>

従来のこの種装置は、第10図に示す如く、文字、図形 等をCCD(Charged-Coupled Device)より成るカメラ21

にて画像化し、この画像入力を2値化回路22で白黒2値化して入力パターンを求め、この入力パターンを画像メモリ23へ格納した後、画像メモリ23中の入力パターンにつき、輪郭追跡回路24を動作させて、輪郭線の追跡処理を実行している。この輪郭追跡処理は、画像メモリ23上に第11図に示すマスク25を設定してこれを所定方向(図中、矢印で示す)へ走査し、各画素につきその画素データSおよびその周囲4方向近傍の画素データS。~S。をチェックし、そのデータ構成に基づき追跡開始点を求めた後、入力パターンの輪郭黒画素を所定方向へ順次追跡してゆく。

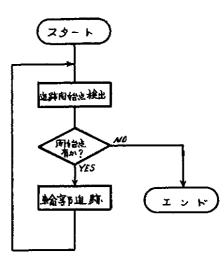

この場合、第1番目の輪郭線につき追跡処理が終了すると、更に前記の走査を再開して、つぎの追跡開始点を検出し、同様の輪郭線追跡処理を実行する。そして全ての輪郭線につき追跡処理が終了して、追跡開始点を発見できなかったとき、輪郭線追跡の全処理を完了させる(第12図のフローチャート参照)。

従って上記従来方式によれば、画像メモリ中に多数の輪郭線が含まれるような場合、各輪郭線にかかる追跡開始点を検出するのに、各走査位置毎にマスク内を5画素アクセスし且つこれを画像メモリの端から端まで実施する必要がある。これがため輪郭追跡処理における追跡開始点の検出処理時間が著しく大きくなり、これが輪郭線追跡の処理効率、ひいてはパターン認識の処理効率を低下させる要因となっている。

## <発明の目的>

本発明は、入力パターンの輪郭線追跡に際し、追跡開始 点の検出を高速化した画像処理装置を提供し、もって輪 郭追跡処理時間の短縮、更にはパターン認識処理効率の 向上をはかることを目的とする。

#### <発明の構成および効果>

上記目的を達成するため、本発明では、入力パターン記憶用の画像メモリに、入力パターンを構成する2値画像データと、輪郭追跡処理時に設定される追跡処理データとして入力パターンの輪郭構成画素に設定される輪郭フラグおよび次の輪郭構成画素への追跡方向に応じて設定されるペアフラグとを、各画素に対応して格納するよう構成し、輪郭追跡開始点の検出処理に際しては、画像メモリを所定方向に走査し各画素を順次アクセスすることにより、各画素の2値画像データおよび追跡処理データを取り込み、これらデータ内容に基づいてアクセス対象画素が輪郭追跡処理済の入力パターンの内外いずれに位置するかを認識すると共に、その認識結果に基づきその画素を輪郭追跡処理の開始点とするか否かを決定するようにした。

本発明によれば、画像メモリを走査して輪郭追跡開始点を検出する場合に、画像メモリの全画素を夫々1回宛アクセスすればよく、輪郭追跡処理における追跡開始点の検出を簡単且つ迅速に実施し得、輪郭線追跡の処理時間を大幅に短縮でき、パターン認識処理の効率を向上し得50

る等、発明目的を達成した顕著な効果を奏する。 <実施例の説明>

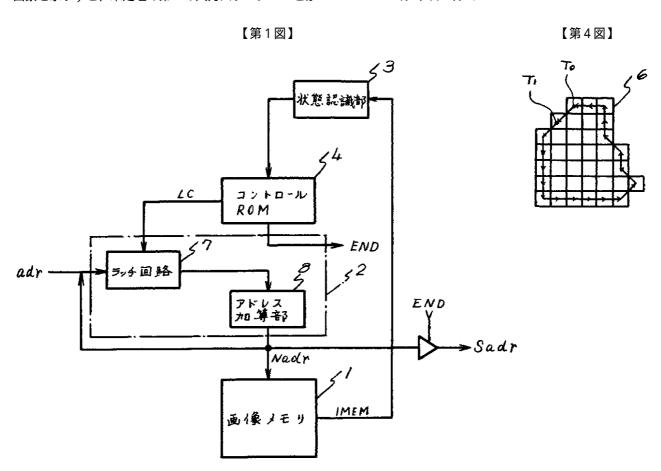

第1図は本発明にかかる画素処理装置の構成例を示す。 図示例の装置は、画像入力を白黒2値化して形成された 入力パターンを縦横複数の画素範囲に格納する画像メモ リ1と、画像メモリ1を所定方向に走査して各画素を順 次アクセスしてゆく走査回路2と、画像メモリ1の各画 素のデータを順次取り込んで現アクセス対象画素のパタ ーン状態を認識するための状態認識部3と、状態認識部 3の認識結果に基づきその画素を輪郭追跡開始点として 検出するか否かを判定するコントロールROM(Read Only Memory)4とから構成されている。

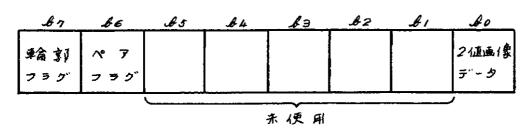

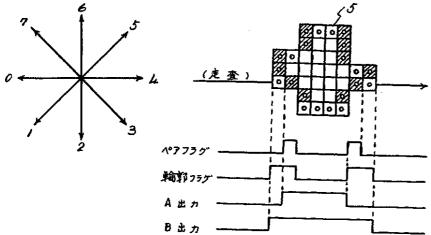

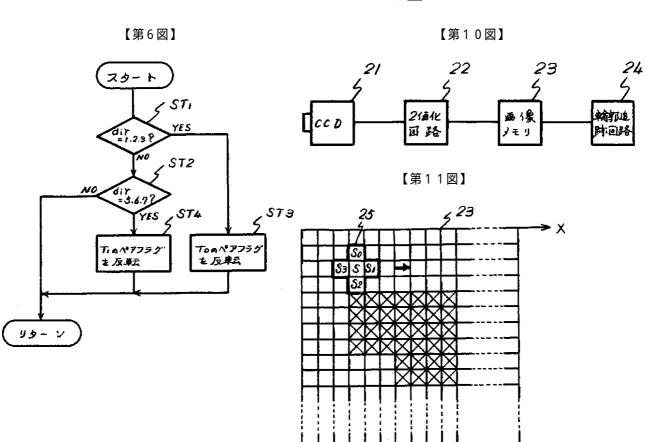

前記画像メモリ1の各画素には、第2図に示すbo~brの 8 ビットデータが格納されるようになっており、本実施 例の場合、0番目のビットb。には2値画像データ(黒画 素が「1」,白画素が「0」)、6番目のビットbaには ペアフラグ(「1」または「0」)、7番目のビットb<sub>7</sub> には輪郭フラグ(輪郭点が「1」, それ以外が「0」) が、夫々セットされる。このペアフラグおよび輪郭フラ グは、輪郭線追跡処理が実行された画素についてのみセ ットされるもので、第3図に示す入力パターン5の場 印の画素に輪郭フラグ「1」が、また斜線 の画素にペアフラグ「1」が夫々セットされている。 第4図乃至第6図は、ペアフラグの設定方法を示してい る。今、第4図に示す入力パターン6につき、図中矢印 で示す如く輪郭線の追跡を実行する場合、ある画素Toか らつぎの画素Tィへ輪郭線を追跡すると、その都度、追跡 方向を第5図に示す8方向コードで規定すると共に、第 6 図に示す手順を実行して、対応画素にペアフラグを立 てる。第6図において、ステップ1(図中、「ST1」の 如く示す)およびステップ2は方向コードdirを判定す るものであり、方向コードdirが1,2,3のいずれか であるとき、ステップ 1 が " YES " となり、追跡元に かかる画素T₀ のペアフラグを反転させる(ステップ 3)。また方向コードdirが5,6,7のいずれかであ るとき、ステップ2が"YES"となり、追跡先にかか る画素T<sub>1</sub>のペアフラグを反転させる(ステップ4)。更 に方向コードdirが0、4のいずれかであるとき、ステ ップ1およびステップ2のいずれもが"NO"となり、 両画素To,Tiのペアフラグはそのままとする。尚各画素 におけるペアフラグはその初期状態では「0」である。 かくて画像メモリ1は、各画素毎に2値画像データ、ペ アフラグ、輪郭フラグを含むデータIMEMが格納されてお り、この画像メモリ1を走査回路にて走査し各画素を順 次アクセスすることにより、各画素のデータIMEMを順次 状態認識部3に取り込む。この場合、前記走査回路で は、最初ラッチ回路7に初期設定アドレスadrをラッチ し、アドレス加算部8にて1加算して、画像メモリ1を アクセスするアドレスNadrを得、以下同様の加算処理を 繰り返して、このアドレスNadrを更新してゆく。

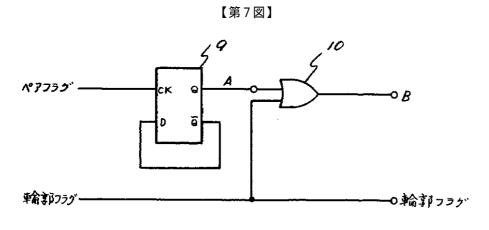

状態認識部3は、現アクセス対象画素がパターン中でど のような状態にあるのかを前記データIMEMに基づき認識 するもので、例えば第7図に示す如く、ペアフラグを入 力してQ端子より符号Aで示す出力を出すフリップフロ ップ9と、A出力および輪郭フラグを入力して符号Bで 示す出力を出すオア回路10とで構成されている。今第 3 図に示す入力パターン 5 を同図の矢印方向に走査した 場合を想定すると、ペアフラグ、輪郭フラグ、A出力、 B出力の各レベルは図に示す如くになり、B出力がパタ 理「1」ならば、入力パターンの内側に、また論理 「0」ならば、入力パターンの外側に、夫々アクセス対

この状態認識部3の認識結果に基づきつぎのコントロー ルROM4は、アクセス対象画素を輪郭追跡開始点として検 出するか否かを判断するもので、もし追跡開始点としな いとき、LC出力をラッチ回路7へ送ってアドレスNadr をラッチし、一方追跡開始点とするときは、END出力 を出し、追跡開始点アドレスSadrを得る。

象画素が位置していると判断できる。

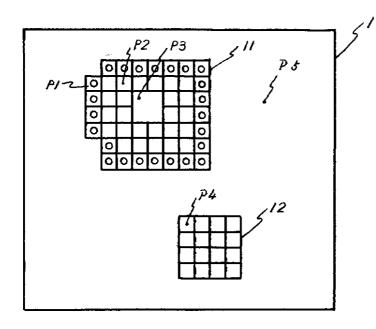

第8図は、上記コントロールROM4における追跡開始点 の判断テーブルを示し、同図中、P1~P5は第9図に示す 画像メモリ1上の各点のP1~P5に対応している。この第 9図に示す画像メモリ1には、輪郭線追跡処理済の第1 の入力パターン 1 1 (図中、 印は輪郭フラグ「1」の 画素を示す)と、未処理の第2の入力パターン12とが\* \* 格納されており、点P1~P3は第1の入力パターン11の 内側に、点 P 4 は第 2 の入力パターン 1 2 の内側に、点 P5は両入力パターン11,12の外側に夫々位置して いる。かくしてコントロールROM4は、B出力、輪郭フ ラグ、2値画像データの内容に基づき上記判断を行なう もので、第8図に示す例では、B出力の論理が「0」、 輪郭フラグが「0」、2値画像データが論理「1」であ る点 P 4 が輪郭追跡開始点として検出される。

### 【図面の簡単な説明】

ーンの状態に対応することがわかる。従ってB出力が論 10 第1図は本発明にかかる2値画像処理装置の構成例を示 す回路ブロック図、第2図は画像メモリの各画素へ格納 されるデータのフォーマットを示す図、第3図は入力パ ターンと各フラグおよび出力との対応関係を示す図、第 4 図は入力パターンの輪郭線追跡処理を説明するための 図、第5図は8方向コードを説明するための図、第6図 はペアフラグ設定処理動作を示すフローチャート、第7 図は状態認識部の具体回路を示す回路図、第8図は追跡 開始点の検出テーブルを示す図、第9図は第8図に対応 する画像メモリ上の各点を示す図、第10図は従来例の 20 装置構成を示すブロック図、第11図は従来例の輪郭追 跡開始点の検出処理を説明するための図、第12図は輪 郭追跡処理を示すフローチャートである。

1...... 画像メモリ、2...... 走査回路

3 ...... 状態認識部

4 ......コントロールROM

【第2図】

【第5図】 【第3図】

【第9図】 【第12図】

【第8図】

|            |   |      |   | 2值画像。画素の值 |    |

|------------|---|------|---|-----------|----|

|            |   |      |   | /         | 0  |

| В          | , | 翰    | 1 | PI        |    |

| <b>a</b> , | Ĺ | ラフラグ | 0 | P2        | РЗ |

| 值          | o | 輪ジラブ | 1 |           |    |

|            |   |      | 0 | PW        | PS |

## フロントページの続き

## (72)発明者 宮宗 宏昭

京都府京都市右京区花園中御門町3番地株式会社立石ライフサイエンス研究所内

(56)参考文献 特開 昭60 - 263276 ( J P , A)